HCMOS晶體振蕩器的倍頻器與乘法器

來源:http://m.ike-digital.com 作者:康華爾電子 2020年06月12

HCMOS晶體振蕩器的倍頻器與乘法器

HCMOS邏輯集成電路產生的快速邊沿含有豐富的諧波,可以有選擇地進行調諧,以制作簡單的倍頻器.可以通過多種方式選擇期望的諧波,但是應該觀察到幾個點.首先,調諧網絡不應給集成電路的輸出端帶來過大的容性負載,建議包括一個串聯限流電阻.其次,應該避免DC路徑接地,以節省電力.第三,網絡應該提供良好的濾波,重點是抑制低頻.

圖1示出了采用兩個HCMOS反相器的簡單乘法器.第一個逆變器產生富含諧波的方波,該方波被施加到電阻分壓器.分壓器確保集成電路不會負載過重,并為后續的串聯調諧電路提供低阻抗,以保持石英晶體振蕩器的品質因數.在這種應用中,調諧電路被調諧到30MHz(倍增系數為5). 通過儲能電感從旁通電容器向后一個柵極提供DC偏置,該旁路電容器充電至V/2.如果選擇電容器在倍頻下具有約1000歐姆的阻抗,則儲罐將具有足夠高的Q.交流門將在較高的頻率下工作良好,但可能需要較低的Q值才能使C的值更大.諧振電感的電抗會降低一些,因為它必須諧振IC輸入的電容(交流電通常約為4pf).這些簡化的方程式包括以下關于1000ohm電抗的假設:

L=160/(f+25x10-9f2)

C=160x10-6/f,其中f是諧波頻率.(增加C并減少L來降低Q.)

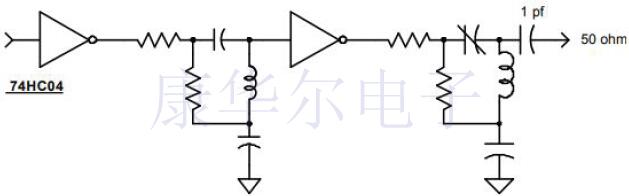

乘法器的輸入和輸出電路將根據應用而變化.如果輸入是大于約1伏p-p的正弦波,則輸入可以簡單地與電阻分壓器電容耦合以偏置柵極.略微偏置偏置電壓,以便在不存在輸入信號的情況下,柵極為高電平或低電平,除非始終存在該信號.可以通過使用調諧阻抗匹配網絡將輸出轉換為正弦波.類似于圖2中所示的諧波選擇網絡的另一個網絡.對于OSC晶振輸出,1是一個不錯的選擇,因為它為輸出門提供了電阻性負載,抑制了低頻,并在串聯諧振電路的中心產生了一個大正弦波.通過將一個非常小的電容器(大約1pf)連接到4.7uh扼流圈的頂部,可以實現低阻抗輸出(50ohms等),如圖2所示. 注意,除非需要兩級乘法,否則輸出網絡將被調諧到與乘法器網絡相同的頻率.如果低電平正弦波足夠,則第二個門可能會被忽略.圖3示出了觸發器如何可以用于同時除法和乘法以獲得分數乘法因子.

圖3:6MHz~7.5MHz乘法器

該合成器使用單個7474觸發器將6MHz輸入轉換為7.5MHz(倍數為1.25).來自石英振蕩器的6MHz方波被觸發器之一分頻,并施加到類似于圖2的網絡上.1.將3MHz(15MHz)的五次諧波除以第二觸發器產生7.5MHz.

圖4示出了使用兩個nand門的門控輸出乘法器.與以前一樣選擇網絡值.當需要在輸出頻率上具有高開關比時,門控乘法器很有用,因為停止乘法過程實際上會消除頻率.為了獲得最佳性能,請選擇同相門,因為當倍頻器關閉時,輸出將通過非常低的阻抗接地,從而減少了來自其他級的諧波通過電源總線進入輸出回路的機會. 這里有一些其他的實驗思路:

通過增加與CMOS輸出串聯的調諧電路,利用CMOS的低輸出阻抗,可以使進入濾波器的饋電點阻抗低得多,從而產生更多的輸出.(串聯諧振電路可防止CMOS在基頻上承受太大的負載.)

幾個門可以并聯以增加輸出.在連接每個輸出之前,請將每個輸出串聯一個小電阻.HCMOS將在低至兩伏的電源電壓下運行,盡管信號會更小且設備速度稍慢,但省電效果將非常明顯.兩個門乘法器的輸出可將兩個輸入饋入異或,或生成和頻或差頻以進行更復雜的合成.四位異或將完成整個工作,而留下一個門來放大輸出.

HCMOS晶體振蕩器的倍頻器與乘法器

HCMOS邏輯集成電路產生的快速邊沿含有豐富的諧波,可以有選擇地進行調諧,以制作簡單的倍頻器.可以通過多種方式選擇期望的諧波,但是應該觀察到幾個點.首先,調諧網絡不應給集成電路的輸出端帶來過大的容性負載,建議包括一個串聯限流電阻.其次,應該避免DC路徑接地,以節省電力.第三,網絡應該提供良好的濾波,重點是抑制低頻.

圖1示出了采用兩個HCMOS反相器的簡單乘法器.第一個逆變器產生富含諧波的方波,該方波被施加到電阻分壓器.分壓器確保集成電路不會負載過重,并為后續的串聯調諧電路提供低阻抗,以保持石英晶體振蕩器的品質因數.在這種應用中,調諧電路被調諧到30MHz(倍增系數為5). 通過儲能電感從旁通電容器向后一個柵極提供DC偏置,該旁路電容器充電至V/2.如果選擇電容器在倍頻下具有約1000歐姆的阻抗,則儲罐將具有足夠高的Q.交流門將在較高的頻率下工作良好,但可能需要較低的Q值才能使C的值更大.諧振電感的電抗會降低一些,因為它必須諧振IC輸入的電容(交流電通常約為4pf).這些簡化的方程式包括以下關于1000ohm電抗的假設:

L=160/(f+25x10-9f2)

C=160x10-6/f,其中f是諧波頻率.(增加C并減少L來降低Q.)

乘法器的輸入和輸出電路將根據應用而變化.如果輸入是大于約1伏p-p的正弦波,則輸入可以簡單地與電阻分壓器電容耦合以偏置柵極.略微偏置偏置電壓,以便在不存在輸入信號的情況下,柵極為高電平或低電平,除非始終存在該信號.可以通過使用調諧阻抗匹配網絡將輸出轉換為正弦波.類似于圖2中所示的諧波選擇網絡的另一個網絡.對于OSC晶振輸出,1是一個不錯的選擇,因為它為輸出門提供了電阻性負載,抑制了低頻,并在串聯諧振電路的中心產生了一個大正弦波.通過將一個非常小的電容器(大約1pf)連接到4.7uh扼流圈的頂部,可以實現低阻抗輸出(50ohms等),如圖2所示. 注意,除非需要兩級乘法,否則輸出網絡將被調諧到與乘法器網絡相同的頻率.如果低電平正弦波足夠,則第二個門可能會被忽略.圖3示出了觸發器如何可以用于同時除法和乘法以獲得分數乘法因子.

圖3:6MHz~7.5MHz乘法器

圖4示出了使用兩個nand門的門控輸出乘法器.與以前一樣選擇網絡值.當需要在輸出頻率上具有高開關比時,門控乘法器很有用,因為停止乘法過程實際上會消除頻率.為了獲得最佳性能,請選擇同相門,因為當倍頻器關閉時,輸出將通過非常低的阻抗接地,從而減少了來自其他級的諧波通過電源總線進入輸出回路的機會. 這里有一些其他的實驗思路:

通過增加與CMOS輸出串聯的調諧電路,利用CMOS的低輸出阻抗,可以使進入濾波器的饋電點阻抗低得多,從而產生更多的輸出.(串聯諧振電路可防止CMOS在基頻上承受太大的負載.)

幾個門可以并聯以增加輸出.在連接每個輸出之前,請將每個輸出串聯一個小電阻.HCMOS將在低至兩伏的電源電壓下運行,盡管信號會更小且設備速度稍慢,但省電效果將非常明顯.兩個門乘法器的輸出可將兩個輸入饋入異或,或生成和頻或差頻以進行更復雜的合成.四位異或將完成整個工作,而留下一個門來放大輸出.

HCMOS晶體振蕩器的倍頻器與乘法器

正在載入評論數據...

相關資訊

- [2024-02-18]CTS汽車級CA系列時鐘振蕩器

- [2024-01-20]TXC晶技5G通信專用小型7050mm恒...

- [2024-01-20]TXC恒溫晶體振蕩器新產品方案發...

- [2023-12-28]關于GEYER格耶品牌產品設計與支...

- [2023-12-28]GEYER格耶電子晶振公司的制品詳...

- [2023-11-06]Wi2Wi品牌發布其新的SN系列晶體...

- [2023-10-13]美國GED高質量時鐘晶體振蕩器

- [2023-09-25]H.ELE從原始石英晶體到精密晶體...

業務經理

業務經理